Enhancing Non-determinism in Operating Systems

A Thesis

Submitted to the Faculty

in partial fulfillment of the requirements for the

degree of

Doctor of Philosophy

by

Morgon Kanter

Thayer School of Engineering

Dartmouth College

Hanover, New Hampshire

October 2013

**Examining Committee:**

Chairman\_\_\_\_\_Stephen Taylor, PhD

Member\_\_\_\_\_\_Sergey Bratus, PhD

Member\_\_\_\_\_ George Cybenko, PhD

Member

Steve Chapin, PhD

F. Jon Kull Dean of Graduate Studies

# Abstract

Computer security has come a long way since the days of the first Internet worm. With the spreading and commercialization of the Internet, the stakes have gotten higher. Viruses existed and spread before most computers were online, but as global networking has spread an interesting new phenomenon has arisen: homogenous computing. Vast swathes of internet-connected computers can be placed into distinct categories such as "Linux 3.1 machines" and "Windows 7 machines", with each category having vulnerabilities that work across the entire class. Thus the Internet has acted as a vulnerability amplifier: if you infect one, you can infect many -- it has never been easier to infect a large number of systems. This thesis aims to raise the difficulty for attackers to spread exploits easily: *increasing the failure rates* associated with using the same exploit across multiple machines, denving surveillance of target machines and binary codes, denying persistence on a target system once it has been exploited, and eliminating common exploitation techniques. These goals are accomplished by enhancing nondeterminism in operating systems: utilizing a hypervisor to refresh microkernels and add restrictions on their operation, adding *diversity* to microkernels and user processes, and adding *camouflage* to network protocols. Collectively these techniques serve to make each running system unique, unpredictable, and difficult to identify.

# Preface

Thanks Steve, as well as fellow group members Colin, Jason, Mike, Rob, and Steve. And of course, my wife Sam.

This research is supported by the Defense Advanced Research Projects Agency as part of the MRC program under contract FA8750-11-2-0257. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the Defense Advanced Research Projects Agency (DARPA) or the U.S. Government.

# **Table of Contents**

| Abstract                                            | ii   |

|-----------------------------------------------------|------|

| Preface                                             | iii  |

| Table of Contents                                   | iv   |

| List of Tables                                      | viii |

| List of Figures                                     | ix   |

| List of Programs                                    | X    |

| 1. Overview                                         | 1    |

| 1.1 Problem                                         | 1    |

| 1.2 Hypothesis                                      | 1    |

| 1.3 Approach                                        | 1    |

| 1.4 Contributions                                   | 2    |

| 1.5 Metrics and Analysis                            | 3    |

| 1.6 Conventions                                     | 4    |

| 1.7 Outline of the Thesis                           | 4    |

| 2. Core Ideas and Related Work                      | 6    |

| 2.1 Threat Model                                    | 6    |

| 2.2 Vulnerabilities and Vulnerability Amplification | 7    |

| 2.3 Stealth and Persistence                         | 9    |

| 2.4 Reverse Engineering                             | 10   |

| 2.5 Protection Mechanisms                           | 11   |

| 2.6 Non-Determinism and Diversity                   | 12   |

| 2.7 Camouflage                                           | 16 |

|----------------------------------------------------------|----|

| 3. Gold-Standard Refresh                                 |    |

| 3.1 Hypervisor Design                                    |    |

| 3.2 Goal 1: Diskless, Read-only Bootstrapping            | 23 |

| 3.2.1 The MBR Bootloader                                 | 25 |

| 3.2.2 The Stage-1 Bootloader                             |    |

| 3.2.3 The Stage-2 Bootloader                             | 27 |

| 3.2.4 PXE Boot                                           |    |

| 3.3 Goal 2: Kernel Refresh, Denying Persistence          |    |

| 3.3.1 Enabling Virtualization                            |    |

| 3.3.2 The Hypervisor Main Loop                           |    |

| 3.3.3 Kernel Environment                                 |    |

| 3.4 Goal 3: MULTICS-style Protections Applied to Kernels |    |

| 3.5 Goal 4: Processor State Protection                   |    |

| 3.6 Attack Surface Minimization                          | 40 |

| 3.7 Supporting Legacy Operating Systems                  | 41 |

| 3.8 Summary                                              | 42 |

| 4. Diversity through Compile-Time Techniques             | 43 |

| 4.1 Implementation                                       | 44 |

| 4.1.1 The Padding Transformation                         | 44 |

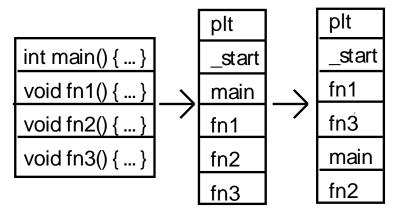

| 4.1.2 The Ordering Transformation                        | 46 |

| 4.2 Quantifying Diversity                                | 47 |

| 4.2.1 Entropy of the Padding Transformation              | 48 |

| 4.2.2 Entropy of the Ordering Transformation | 50 |

|----------------------------------------------|----|

| 4.2.3 Joint Entropy of the Transformations   | 51 |

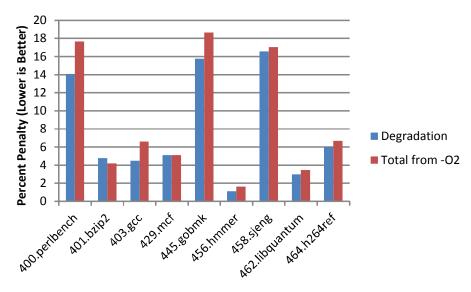

| 4.3 Performance Impact                       | 55 |

| 4.4 Adoption Challenges                      |    |

| 4.5 Summary                                  | 57 |

| 5. Diversity through Runtime Techniques      | 59 |

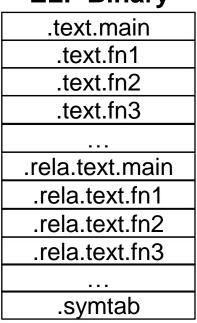

| 5.1 ELF Preliminaries                        | 59 |

| 5.1.1 Binary Layout                          | 59 |

| 5.1.2 The Symbol Table                       | 61 |

| 5.1.3 Relocations                            |    |

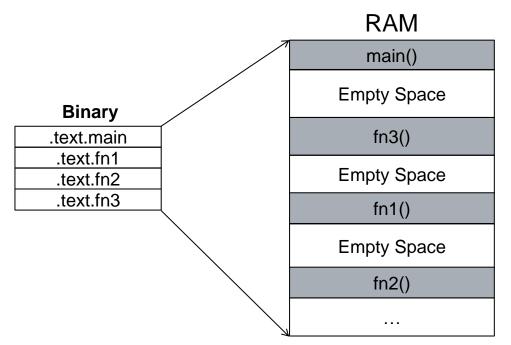

| 5.2 Implementation                           | 63 |

| 5.3 Analysis                                 | 67 |

| 5.3.1 Performance Impact                     |    |

| 5.3.2 Code Size Impact                       | 70 |

| 6. A Hybrid Technique                        | 71 |

| 6.1 Replication                              |    |

| 6.2 Discussion                               | 74 |

| 6.3 Summary                                  | 75 |

| 7. Hiding by Camouflage                      | 77 |

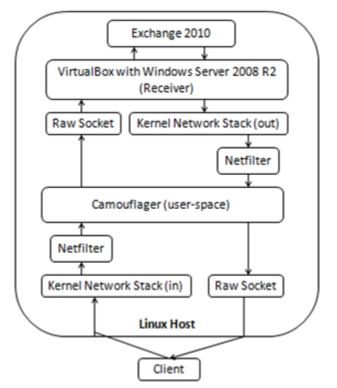

| 7.1 Implementation                           |    |

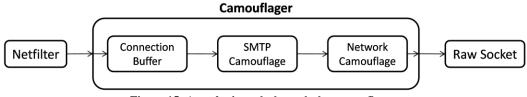

| 7.1.1 Application Layer Camouflage           | 80 |

| 7.1.2 Network Layer Camouflage               |    |

| 7.2 Lessons Learned                          |    |

| 7.3 SMTP Session Example                              |     |

|-------------------------------------------------------|-----|

| 7.4 Results                                           | 95  |

| 7.5 Costs and Future Work                             | 96  |

| 7.6 Summary                                           | 97  |

| 8. Conclusions                                        |     |

| 8.1 The Four Aspects                                  |     |

| 8.2 Future Work                                       |     |

| Appendix A. Virtual Memory and Processor State in x86 |     |

| Appendix B. VMCS Fields                               |     |

| References                                            | 118 |

# List of Tables

| Table 1: Code size                                                     | 40  |

|------------------------------------------------------------------------|-----|

| Table 2: Padding entropy                                               | 50  |

| Table 3: All combinations of two instructions with two transformations | 52  |

| Table 4: Entropy estimation of combined transformations                | 54  |

| Table 5: Minimal entropy estimation for combined transformations       | 55  |

| Table 6: Average code size increase (in kilobytes and %)               | 57  |

| Table 7: Flags in Control Register 0                                   | 109 |

| Table 8: Flags in Control Register 4                                   | 110 |

| Table 9: Flags in EFER                                                 | 111 |

| Table 10: Pin-Based VM Execution Controls field                        | 114 |

| Table 11: Primary Processor-Based VM Execution Controls field          | 115 |

| Table 12: Secondary Processor-Based VM Execution Controls field        | 116 |

# List of Figures

| Figure 1: Exploitation threat model                                  | 6  |

|----------------------------------------------------------------------|----|

| Figure 2: The Bear operating system layers                           | 19 |

| Figure 3: Bootstrapping the hypervisor                               | 24 |

| Figure 4: Illustration of the IBM-Compatible MBR and partition table | 25 |

| Figure 5: Illustration of Extended Page Tables                       | 36 |

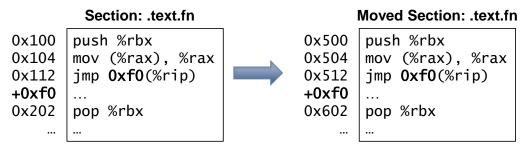

| Figure 6: Function with two vacuous-padded variants                  | 46 |

| Figure 7: Function layout after compiling and linking                | 47 |

| Figure 8: Benchmark results for vacuous code padding                 | 56 |

| Figure 9: ELF binary, section view                                   | 61 |

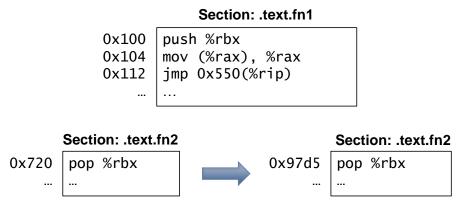

| Figure 10: Example binary and corresponding loader diversification   | 64 |

| Figure 11: Control flow within same diversity unit                   | 65 |

| Figure 12: Control flow between two different diversity units        | 65 |

| Figure 13: Hybrid diversity system                                   | 71 |

| Figure 14: Overview of system internals                              | 79 |

| Figure 15: A packet's path through the camouflager                   | 80 |

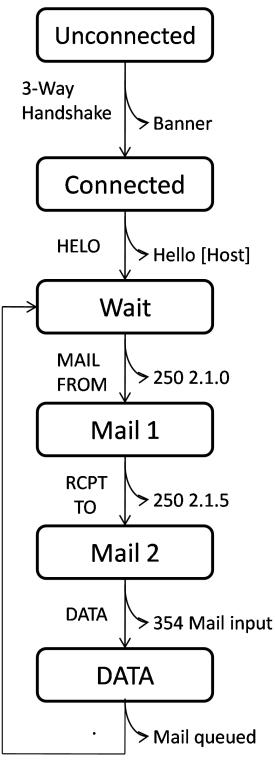

| Figure 16: State machine representation of SMTP common path          | 82 |

# List of Abstract Programs

| Program 1: Enabling virtualization          | 30 |

|---------------------------------------------|----|

| Program 2: The hypervisor main loop         | 31 |

| Program 3: Handling memory violations       | 38 |

| Program 4: The padding transformation       | 46 |

| Program 5: The diversifying loading process | 67 |

# **Chapter 1: Overview**

# 1.1 Problem

How can we increase attacker workload to reduce the incidence of computer network attacks against critical infrastructure?

# **1.2 Hypothesis**

A radical increase in non-determinism within operating systems can require increased attacker time, effort, and failure, requiring increased levels of attacker sophistication.

## 1.3 Approach

This thesis introduces non-determinism through four core mechanisms:

- *Gold-standard Refresh:* Random refresh of potentially compromised system components (e.g. microkernel, device drivers, etc) to remove an adversary's ability to persist over long durations; this also has the effect of invalidating surveillance information associated with the operating system signature, essential in determining the available vulnerabilities.

- *Compile-Time Diversity:* Introduction of non-determinism into sourcecode at compile time to throttle vulnerability amplification, ensuring that the same vulnerability cannot be used in multiple copies of the code.

- *Run-Time Diversity:* Dynamic replication and randomization of code at load time refresh to undermine reverse engineering and further invalidate surveillance.

- Camouflage: Disguising an operating system to appear as an alternative

system, with different vulnerabilities, to complicate system identification.

The combination of these techniques produces a new form of operating system that *increases attacker workload* over multiple complementary dimensions making it significantly more difficult to determine the vulnerabilities present on a system, apply the same attack to multiple hosts, and establish a long-lived presence on a system to achieve effects.

### **1.4 Contributions**

The core contributions of this thesis are:

- A novel, minimalist hypervisor capable of non-deterministically refreshing and diversifying a hosted kernel; kernels may in turn use the same techniques to refresh user code and potentially compromised device drivers [1].

- Compile-time techniques for introducing *static* diversity into operating systems and user code [2].

- Run-time techniques that add *temporal* diversity when combined with refresh [3].

- A hybrid approach that combines compile-time and run-time diversity with *replication* to radically increase the degree of non-determinacy in systems. This approach has modest overhead in performance and code size [3].

- Analytical models that quantify the level of non-determinism induced by diversity [2, 3].

• Application layer techniques that camouflage servers by modifying their network traffic signatures [4].

These systems and techniques have been demonstrated in proof-of-concept implementations and exemplars. The hypervisor has been implemented on multicore blade servers and Dell XPS workstations, supporting both a custom microkernel and the BSD operating system. The compile-time techniques have been implemented as a Clang compiler plugin and demonstrated by diversifying the microkernel, an industrial strength web server (lighttpd), and the SPEC benchmark suite. The run-time techniques have been incorporated into the hypervisor and microkernel loader used to execute the microkernel and user processes. Finally, the camouflage techniques have been used to circumvent common network scanners, such as nmap [5] and Nessus [6], disguising a Microsoft Exchange running on Windows 2008 Server as Sendmail running on Linux 2.6.

# **1.5 Metrics and Analysis**

Unfortunately, it is not practical to directly assess the increase in attacker workload, as it is dependent on a number of subjective factors that include:

- The available manpower and level of expertise of the attacker.

- The creativity of the attacker.

- The type and level of vulnerability of the target system.

- The availability of multiple access paths, e.g. remote exploits, privilege escalations, supply chain access, RF paths, etc.

As an alternative, this thesis therefore focuses on the degree of unpredictability induced in systems and quantifies this through the analytical use of *entropy*. Unfortunately, not all of the techniques admit to direct measurement and thus constructive argument is used in their place where appropriate. These arguments are based on the added steps required to achieve a point of presence, or the increase in technical sophistication required to overcome a particular barrier.

#### **1.6 Conventions**

At several points throughout this thesis, abstract code is used to describe a process. In this abstract code, a **BOLD**, **ALL CAPS** word represents an assembly instruction. A "<-" mark represents the storing of some value. A line beginning with a "//" is a descriptive comment on the current stage of the process.

# **1.7 Outline of the Thesis**

The structure of the thesis is divided into seven chapters:

Chapter 2 introduces the threat model, core ideas, and related research associated with vulnerabilities and their mitigation. This serves to provide background and motivation for the remainder of the thesis.

Chapter 3 describes the hypervisor, created as a part of this thesis. It describes the design philosophy and the specific details of its inner workings, along with bootstrapping details. It also introduces the fundamental protections provided by the hypervisor to running kernels.

Chapter 4 describes the compile-time techniques developed in the thesis and analyzes the level of diversity that can be obtained along with the associated overhead. Chapter 5 describes the run-time techniques incorporated into the loader and integrated within the hypervisor and kernel. These techniques are contrasted with the compile-time techniques in Chapter 4 and analysis quantifies the gain in diversity and performance.

Chapter 6 develops a hybrid model that combines the methods in Chapters 4 and 5 and analyses the combined technique. Code replication is then added to further increase non-determinism.

Chapter 7 introduces network camouflage and describes how it operates on the system network stack.

Chapter 8 concludes the thesis, mapping out directions for future research and lessons learned.

# **Chapter 2: Core Ideas and Related Work**

## 2.1 Threat Model

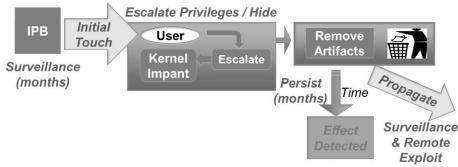

In order to provide context for the work presented in this thesis, it is useful to provide a general threat model for network attacks involving remote control [7]. The model used here is presented in Figure 1 and combines typical activities taken from a broad variety of attack classes. The threat may involve several steps including <u>surveillance</u> to determine if a vulnerability exists [8], use of an appropriate exploit or other access method to establish an implant [8], privilege escalation where possible [9], removal of exploit artifacts, and hiding behavior [10]. Surveillance may involve obtaining a copy of the targets binary code and using <u>reverse engineering</u> [11,12] or fuzzing [13] to locate additional vulnerabilities to facilitate a broad range of attack vectors, including return oriented programming [14]. The implant then <u>persists</u> for a time sufficient enough to carry out some malicious effect, obtain useful information, or propagate intrusion to other systems.

Figure 1: Exploitation threat model.

Unlike the time to execute an exploit, the time spent in surveillance and persistence may range from minutes to months or even years depending upon the intended effect. Moreover, the presence of an intrusion may *never* be detected by network defenses but instead may be recognized indirectly due to either a deviation from expected behavior, or may be derived from intelligence sources.

### 2.2 Vulnerabilities and Vulnerability Amplification

The history of network intrusions, employing differing elements of the model presented in Section 2.1, has been a continual arms race between defenders and attackers: Vulnerabilities are revealed in hardware and software systems, attackers develop exploit techniques to take advantage of them, eventually the attacks are discovered and defenders develop appropriate protections and patches. Subsequently, more advanced exploits that bypass the protections are introduced and the cycle begins anew.

Buffer overflow attacks provide the most widely recognized example of this pattern [15]. A complete description of the technique, along with how to identify a vulnerability and exploit it, can be found in [16]. The essence of the idea is to overrun a programming buffer with unexpected input so as to cause installed software to make an unintended transfer of control; typically to implanted attack code (often termed "shell code"). Since discovery of this form of attack, a variety of solutions<sup>1</sup> have been developed to specifically mitigate this

<sup>&</sup>lt;sup>1</sup> A survey of available protections, as well as more details on buffer overflow techniques, can be found in [17].

particular form of vulnerability. Intel, for example, introduced the *no-execute bit* for page tables, also known as *Data Execution Prevention* (DEP). This concept, taken from the MULTICS [18] system, provides a mechanism that allows operating system developers to ensure that memory is either *writable* or *executable*, but never *both simultaneously*. There are not only hardware solutions – software solutions have also been invented, such as runtime size checks for buffers utilized on the stack [19].

Unfortunately, the advent of DEP and other solutions led to the development of alternative exploitation techniques, which bypass the protection. Some of the first attacks designed against DEP merely directed the running process to call functions provided by the operating system to disable the protections; they then proceeded with the classic buffer overflow [20]. These functions seem insecure at first glance, but are actually useful: Some applications require the same piece of memory to be both writable and executable. One such application is a just-in-time compiler: It compiles (*writes*) a high-level programming language to machine code and then *executes* it. Just like a binary loaded from disk, the compiled code must be stored in memory at some location before it is placed onto the processor for execution.

Eventually, attacks that bypass DEP execution prevention were generalized. If a system function for disabling protections could be called, why not call some other library function instead? This became known as the *return-tolibc* attack [21]. It then became clear that if an arbitrary library function could be invoked, other chunks of pre-existing code could also be used. These chunks need not necessarily be complete functions, but rather small assembly fragments already loaded onto the system. These chunks, known as gadgets [22], can perform some small amount of computation (add, multiply, compare), and then redirect system control flow based on computed data written in the process address space. The most prevalent opportunity to transfer control was provided by the *ret* (return) assembly instruction available throughout operating system images to return from functions. This instruction uses the system stack to determine which address the processor should jump to, a convenient location to store redirections. This form of exploit was named *return-oriented programming* (ROP) [22]. Although it may not immediately appear particularly useful, a large codebase such as the C programming library (libc), linked to every user process on the system, contains a sufficient number of gadgets to be Turing-complete [23], allowing *any* arbitrary program to be executed. A large set of gadgets is not even required for many common exploitation tasks, such as the disabling DEP, and even programs as small as /bin/true (without use of the linked C library) can be exploited in this fashion [23].

Unfortunately, the fact that relatively few varieties of operating systems are available world-wide, compared to the number of installed systems, *amplifies* the impact of these vulnerabilities: A single exploit can often be employed against a huge number of unpatched systems. Moreover, the increasing prevalence of cloud computing tends to enhance this amplification by radically diminishing the variety of installed system variants.

# 2.3 Stealth and Persistence

9

Once a vulnerability has been discovered and an exploit developed, it is possible to establish a remote point-of-presence, similar to a remote shell. A common next step is to remove the forensic trail associated with access by deleting files, modifying registry keys, etc., and hide any on-host activity. This job is often performed by a *rootkit* – a program delivered by the exploit and operated unwittingly by the infected machine. One of the oldest stealth techniques is to bundle, with the rootkit, programs that replace common system administration programs [10]. For example, the *ps* program lists all processes running on a system, but the rootkit's version of *ps* would fail to report the presence of the rootkit. This technique eventually gave way to returning *false* values for system calls that *ps* would use to gather the list of processes, bypassing the need for replacement programs [10].

Once a rootkit is resident on the system, how does it *persist*? If it exists purely in volatile memory, such as a modification to the running kernel code, it will be removed upon a system reboot. The rootkit thus must have some other residence in non-volatile storage. The hard disk provides the oldest known example [24], but some hardware contains non-volatile memory that can be modified with proper system privileges [25]. To survive any kind of refresh like a reboot without the system being exploited anew, the rootkit must utilize one of these devices.

# 2.4 Reverse Engineering

It is possible that an attacker may have access to a copy of the source code for some or all of a system, it might be *open source code*, or might be provided by an *insider*. Alternatively, the point-of-presence established in Section 2.1 might be used to extract a copy of the running binary code directly from memory.

Having obtained the source code, it is then possible to reverse engineer it to discover vulnerabilities and develop additional exploits. Buffer overflows and other memory corruption attacks require knowledge of the distance between the vulnerable data and the interesting parts of the stack. Return-to-libc attacks require knowledge of the location in memory of the desired functions. Returnoriented programming requires knowledge of desirable gadgets. All of this information can be discovered either through either *static* analysis -- offline disassembly and reverse engineering the addresses at rest -- or *dynamic* analysis can also provide insights into how the attacker might best hide their tracks, or interrupt and resume normal operation of the system via important addresses in the code. A wide variety of tools are available to conduct this analysis, including simple disassemblers like objdump [26] and complex tools such as IDA Pro [11].

#### 2.5 Protection Mechanisms

Many of the fundamental concepts now used to protect operating systems are derived from the engineering principals of *separating concerns* and *encapsulation* embodied in the MULTICs operating system [18]. This resulted in several innovations including the division of an operating system into layers, or *protected rings*, through hardware mechanisms that separate user processes from the system kernel and each other. MULTIC's also included the concept of *read/write/execute* protection bits on memory segments, where each segment maintains independent access controls and a fault is generated if software violates the protections. Read and write access controls subsequently became commonplace in hardware platforms such as the Intel x86 processors. Execute protection has only recently regained currency through the x86-64 platform via the introduction of a *no-execute bit* into 64-bit page table entries [27].

Although techniques have been found to bypass basic protections on occasion, their utility as an organizing principal and a first line of defense cannot be overstated. With the advent of *return-to-libc* attacks and *return-oriented programming*, the presence of basic protections allowed the development of techniques to specifically target these advancements in exploitation independently. For example, compiler-techniques were developed to mitigate return oriented programming by scrubbing usable gadgets out of the assembly process [28-29].

The continual arms race between exploit and mitigation calls into question the entire approach associated with detecting intrusions or reacting to discovery, through sensors, patches, and defense tool rules. In this situation, the defender is always forced to react to the attacker and takes few proactive steps to undermine an attacker's actions before they are known. Instead, this thesis proposes to focus on *increasing attacker workload* by complicating each of the component activities encapsulated in the thread model.

## 2.6 Non-Determinism and Diversity

Cohen [30] and Forrest et al [31] have discussed ideas for using nondeterminism to prevent exploitation. In addition, Forrest has implemented a basic stack frame space randomizer which, while minimal, was sufficient to disrupt many buffer overflow exploits. Unfortunately, no concrete metrics are provided to quantify the level of effective diversity.

The most prominent approach that has evolved is Address Space Layout Randomization (ASLR), developed by the Linux PaX team [32] and later used in many other operating systems including variants of Windows. This technique introduces diversity by randomly relocating the base address of libraries, program text, stack, and heap, at runtime, though it does not attempt to perform any reordering or randomization *within* these memory segments. This removes the ability for attackers to statically pre-determine the address of functions and gadgets used to build exploits or arbitrary code fragments – denying *surveillance*, rather than eliminating the vulnerabilities themselves.

ASLR is believed to be effective against both return-to-libc attacks and return-oriented programming. Unfortunately, a minimal level of entropy is required to protect against brute-force attacks [33]. Early analytical work to quantify the impact on attacker workload has already been conducted; it concludes that approximately 16-bits of entropy, corresponding to 65,536 unique code addresses within a process image, are required to protect against brute force attacks within reasonable timeframes i.e. 20 minutes. There also exist methods to eliminate address space randomness through techniques that bypass the ASLR implementation altogether using specially crafted format strings [34]. It is interesting to note that ASLR was developed *before* the advent of return-oriented programming as a general mitigation against static analysis. This speaks well of the general approach of introducing diversity to deny surveillance.

13

Other work has also been performed in the space of diversity: Instruction Set Randomization encrypts the executable code and grants a level of entropy equal to the strength of the encryption [35]. Unlike the research described here, this approach requires architecture support for some form of emulation [36], or virtualization [37]. The diversity approach described in this thesis has none of these restrictions and can be strengthened by additional techniques including memory encryption [7,38], hardware hiding [39], and nondeterministic refresh; however, it does require access to *source code*.

Tanenbaum has used an alternative approach to protect kernel data structures [40]. Unfortunately, his work uses compartmentalization and modularization of code limited to microkernel designs. While this research involves a microkernel, it targets more than just kernel data structures; the ideas can also be applied to user processes and device drivers. Device drivers are especially problematic, as they contain error rates up to seven times higher than the rest of kernel code [41].

Several authors have examined the use of diversity to directly modify binaries on disk. For example, Pappas et al [42] developed a tool that would diversify compiled binaries by modifying instructions: this removes the immediate vulnerability (while introducing new gadgets) and denies offline surveillance, but would not protect against an attacker that successfully obtains a copy of the diversified binary; the research described in this thesis would also defend against such surveillance. Similarly, Kil et al [43] developed a tool to diversify binaries by relocating segments and reordering within segments, but the code within the segments is unchanged. This work has the same weakness as the tool developed by Pappas et al.

Some researchers have examined diversity, not to deny surveillance, but to specifically disrupt return-oriented programming. In an upcoming paper at the 2013 International Symposium on Code Generation and Optimization, Larsen et al present a diversification scheme at the compiler level that modifies the instruction generation algorithm to remove gadgets, entirely preventing their emission by the compiler. This has no value in denying surveillance, and instead *only* targets return-oriented programming. This thesis does not perform any gadget removal: instead, it aims to increase the unpredictability of *all* addresses. This disrupts the positioning of gadgets, denying surveillance, but does not itself change the instruction stream or program semantics.

Other diversification techniques have been introduced that are similar to the work described in Chapter 4 and 5. Kil et. al. include a similar method of function reordering in their own binary rewriting tool [43]. The method described in this thesis, on the other hand, implements this functionality directly in the linker (for Chapter 4) and at runtime (for Chapter 5) to deny surveillance. kGuard [44] uses a similar technique of padding the start of functions, an operation used in this thesis and described in Chapter 4. However, they only do this to protect and diversify the kernel, not user applications. Furthermore they use a NOP sled to change address locations. The work described in Chapter 4 specifically uses random data, so that any jump attempt will likely crash immediately. While ASLR by default does not randomize within the text segment, this feature was eventually introduced with the Code Islands technique in [45]. This utilizes several similar features to our run-time diversity system; however, the work described in Chapter 5 is not bound by the legacy requirements of the Linux operating system and thus does not suffer the same performance penalties with dynamic linking; it is also used to protect the operating system itself.

### 2.7 Camouflage

One method of surveillance is to use a *network scanner*, such as nmap [5] or Nessus [6]. These scanners can detect which software and operating systems are running on target machines, as well as their specific versions. This fingerprinting effectively provides an attacker with a roadmap of how to exploit the machine. This thesis presents a method for denying surveillance directly through *network camouflage*.

Fingerprinting is possible by virtue of the differences in network- and application-layer protocol implementations for different operating systems. The protocol specifications typically leave many implementation details up to the developer. This allows for multiple implementation strategies and ideas to be used in alternative products. When these design details diverge between competing systems, the differences can be observed by merely using the protocol. Nmap and Nessus both exploit the differences in implementation details for their fingerprinting process. For example, for operating system detection they have databases specifying which details are expected on which system. By examining the response to TCP/IP traffic, they discern which operating system the responses must have originated from. Similar systems exist for application-layer protocols in Nessus [46].

Since service detection is performed by examining implementation differences, it is possible to deny surveillance by modifying these differences. Early uses of this idea, implemented in Morph [47], were able to transparently camouflage a system to appear as Windows 2000, OpenBSD, or Linux 2.4. The concept has also been used in FreeBSD, which scrubs its fingerprint so that it is not detectable by scanners [48]. Linux 2.4 provides a program called IP Personality that allows it to take on alternative operating system characteristics [49]. All of these packages focus on manipulating TCP/IP protocol details to prevent operating system detection. Unlike these solutions, this thesis focuses on denying surveillance of *both* the TCP/IP protocol, to prevent OS-level fingerprinting, and the application layer, to prevent discovery of the specific programs being run on the server.

# **Chapter 3: Gold-Standard Refresh**

To explore the ideas non-deterministic refresh, code diversity, and camouflage it is useful to consider how these techniques might form the basis for a from-scratch operating system design. Current operating system designs have sought to utilize a *static* base of trust and extend trust into software through deliberate layering [50]. A wide variety of vulnerabilities have appeared that undermine kernel security allowing attackers to implant code, hide, and persist at the highest levels of privilege [51]. Furthermore, studies of open source code have indicated that the number of vulnerabilities is directly correlated with the size of the code base [52], indicating that there is substantial value in the intellectual process of *reducing the attack surface*.

The approach described here assumes that adversaries will conduct surveillance, will be successful in gaining access, and will persist undetected. To mitigate the risks associated with remote control, the current kernel, user processes, and device drivers are periodically *discarded*. This can be achieved when they are momentarily not in use, through a collaborative program of interruption, or just prior to the onset of a tactical operation. They are replaced by new instances, bootstrapped in the background from *read-only gold standards*. The cumulative effect of this change in design style is to *increase attacker workload* by continually invalidating surveillance data and denying persistence over time-scales consistent with tactical missions. Unlike other approaches to computer security [53], no attempt is made to detect intrusions: instead, this research focuses on continually validating, preserving, and re-establishing the ability of a mission to proceed. The intent is to cause the attacker to take more time, make more errors, and force attack actions outside the OODA loop of the defender; effectively removing the threat without directly confronting it.

These concepts have been incorporated into a new, from-scratch operating system design – Bear – which operates on 64-bit, x86 multi-core blade servers, and Dell workstations. The full system is depicted in Figure 2 and is composed of a minimalist micro-kernel with an associated hypervisor that shares code extensively to explicitly reduce the attack surface. The micro-kernel also operates independently on ARM M3, M4, A8, and A9 processors.

| User         | User<br>Processes              | rMP                |          | Network<br>Stack |    | Drivers                 |

|--------------|--------------------------------|--------------------|----------|------------------|----|-------------------------|

|              | Message-Passing API            |                    |          |                  |    |                         |

| Micro-kernel | Page<br>Tables<br>(R/W/X)      | Process<br>Refresh |          | Scheduler        |    | System<br>Task          |

| Hypervisor   | Ext. Page<br>Tables<br>(R/W/X) |                    | Kernel I | Refresh          | Tı | rusted File<br>Store    |

| Hardware     | x86-64                         | x86-64 x8          |          | Netwo<br>Card    |    | Interrupt<br>Controller |

Figure 2: The Bear operating system layers.

The core functions of scheduling user processes and protecting them from each other are handled by the micro-kernel [1]. All processes and layers are hardened by strictly enforcing MULTICS-style read, write, and execute protections [18] using 64-bit x86 address translation hardware. Similarly, the hypervisor enforces these protections on kernels. This calculated reduction in versatility is unlikely to impact military applications but explicitly removes vulnerabilities associated with code execution from the heap or stack. All potentially contaminated user processes, device drivers and services are executed with user–level privileges and are strictly isolated from the micro-kernel via a message-passing interface. The system task, executing with kernel privileges, mediates between processes and the kernel to implement the interface. Unlike a conventional rendezvous mechanism [54], this asynchronous, buffered design provides a single uniform treatment of system calls, inter-process, and interprocessor communication. The interface also supports distributed computing through an MPI-like [55] programming model that maps processes to processors using a user level demon, rMP.

To prevent persistence in the micro-kernel, it is non-deterministically refreshed from a gold-standard image in the trusted file store by the *hypervisor* [56]. This store is currently realized through a read-only RAM-disk accessible only from the kernel and hypervisor; however, it could alternatively be realized via read-only memory (ROM) or via an out-of-band, write-enabled channel to flash on new hardware. This minimalist hypervisor design supports *only* the operations required to bootstrap a new micro-kernel and change its network properties (e.g. IP & MAC address) so as to invalidate an adversary's surveillance data. It is significantly different from traditional hypervisors that aim to support a general virtual machine execution environment [57-59], admits to considerable code sharing with the microkernel, and represents a substantial reduction in the system attack surface [1]. The PXE-boot based bootstrapping process

incorporated into the hypervisor applies diversifying transformations to each new kernel. This ensures that every kernel is unique in terms of its addresses, throttling vulnerability amplification and rendering prior surveillance obsolete. The current running and bootstrapping instances of the micro-kernel are isolated in hardware through extended page tables, implemented with Intel Vt-x extensions. Similarly, the network driver is isolated through a mapping scheme based on Intel VT-d extensions.

To prevent persistence in compromised device drivers and services, the micro-kernel randomly and non-deterministically regenerates them from goldstandard images resident in a trusted read-only file store. This process is achieved using the same diversity transformations applied by the hypervisor. Unlike the MINIX re-incarnation process [54], regeneration is carried out without regard to the perceived fault or infection status. User processes can also be refreshed through pre-arranged or designated schedules; for example, every few hours, at night, or just prior to a tactical mission.

The diversification techniques described in this research are applied every time any component of the Bear system is refreshed: when the hypervisor reloads a kernel or when the kernel reloads a device driver or user process. As a result, even if an adversary were to obtain a copy of the entire binary code at any point in time, and invest the effort to reverse engineer it to find vulnerabilities, by the time those vulnerabilities could be exploited the entire address space of the system would have changed and any existing persistent presence eliminated.

21

### **3.1 Hypervisor Design**

The Bear includes a novel hypervisor has incorporates six core design goals:

- 1. Diskless, Read-only Bootstrapping.

- 2. Non-deterministic Kernel Refresh, Denying Persistence.

- 3. MULTICS-style Protections Applied to Kernels.

- 4. Processor State Protection.

- 5. Attack Surface Minimization.

- 6. Kernel Diversity, Denying Surveillance and Throttling Vulnerability Amplification.

This chapter describes the realization of Goals 1 through 5; Goal 6, related to diversity, is covered in Chapters 4 and 5. For now, it is important to simply recognize that the hypervisor diversifies kernels and processes whenever they are reloaded.

The hypervisor was developed to support *only* the core goals. Unlike popular systems such as KVM, Xen, and VMWare, it is *not* designed to provide a generic virtualization environment capable of supporting arbitrary systems. Although the Bear micro-kernel has also been implemented on ARM architectures, the hypervisor only operates on the x86-64 platform using its VT-x hardware support for virtualization. This platform uses several structures and ideas for processor control and memory protection, such as the CR0 and CR4 registers, real mode, protected mode, long mode, segmentation, GDT and LDT. Appendix A includes more information on these structures and their use, for those who lack familiarity with the basic platforms. The remainder of this chapter is devoted to the inner workings of the hypervisor. These details operate collectively at the lowest level of the system to realize the six core goals. The system bootstrap process is described first, followed by the enabling of virtualization, and the hypervisor's main loop. With the groundwork of the hypervisor detailed this chapter then discusses how virtualization can be used to protect kernels and other design considerations used in creating the system.

## 3.2 Goal 1: Diskless, Read-only Bootstrapping

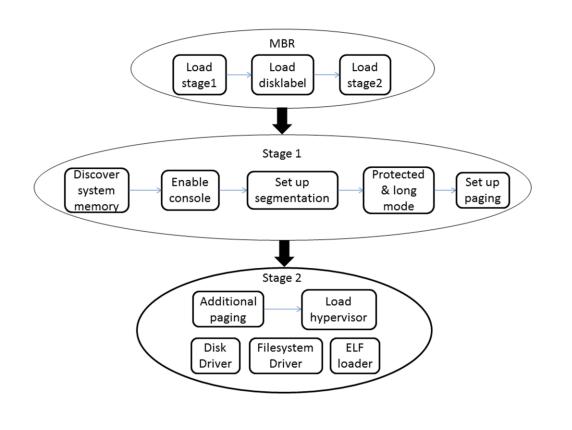

The hypervisor bootstrap process takes the system from a powered-off state to a running hypervisor. It must load all necessary system image files, set up memory protections, and enter *long mode* -- a protected processor state required to enforce memory protection. Most modern operating systems use long mode; however, few enter this mode directly, instead operating initially in an unprotected and vulnerable *real mode* during bootstrapping to support legacy capabilities. Circumventing this legacy support with a from-scratch design not only simplifies bootstrapping but also reduces the vulnerable time in real mode. Figure 3 provides a simplified overview of the entire bootstrapping process. It contains three concrete stages that incrementally built and protect the system: MBR, Stage-1, and Stage-2 bootloaders. Each stage is circled, and lists the specific tasks performed by the stage.

Figure 3: Bootstrapping the hypervisor.

The Bear bootstrapping process has emerged through two iterations to support the goal of diskless read-only bootstrapping. The first iteration used a simple Fat file system accessing a physical hard disk on the machine, addressed using the IDE standard. The second iteration uses the PXE boot standard to transfer a read-only image to a RAM-disk on the machine; the Fat file system is then used to access the RAM-disk containing the system executables. The file system does not provide a write operation and can only read data from read-only protected memory pages. To minimalize code changes, the images transferred in the bootstrap process are identical to those used in the original design. They are deposited at the PXE-boot server after compilation, providing a natural hook for encryption of the binaries.

# 3.2.1 The MBR Bootloader

The "IBM compatible" label associated with personal computers dating back to the 1980s includes a *boot loader standard* still used by most modern operating systems: Upon system start, the first 512 bytes of a bootable hard disk, called the Master Boot Record (MBR), is loaded at physical address 0x7c00. The MBR contains the code for the initial section of a bootloader. The MBR also contains a partition table, which defines the layout of the rest of the physical disk, and a two-byte signature. The structure of the MBR is shown in Figure 4.

| 0               | 446 5           | 10 512   |

|-----------------|-----------------|----------|

| Bootloader Code | Partition Table | 55<br>AA |

|            | Size    | Description                              |

|------------|---------|------------------------------------------|

|            | 1 byte  | Bootable flag (0x80 = bootable, 0 = non) |

|            | 1 byte  | Starting head <sup>+</sup>               |

|            | 6 bits  | Starting sector <sup>+</sup>             |

|            | 10 bits | Starting cylinder <sup>+</sup>           |

| 16 bytes — | 1 byte  | System ID†                               |

|            | 1 byte  | Ending head†                             |

|            | 6 bits  | Ending sector <sup>+</sup>               |

|            | 10 bits | Ending cylinder†                         |

|            | 4 bytes | LBA of partition start                   |

|            | 4 bytes | Partition size in sectors                |

Partition Table Entry (four per table)

Figure 4: Illustration of the IBM-compatible MBR and partition table.

The elements marked † in the partition table correspond to a Cylinder-Head-Sector method of addressing data on disk that are no longer used. Modern systems, including Bear, instead use Logical Block Addressing (LBA) in which 512-byte *sectors* are laid out linearly on disk. For example, the 655th sector would correspond to the data on disk ranging from bytes 655(512) to 656(512)-1.

Once the MBR is read into memory, the processor then begins execution at address 0x7c00, the location of the *MBR bootloader code*. At this point, there is no form of memory protection and the processor is in *real mode*.

The MBR bootloader is, of necessity, simple due to space constraints; since it must share the MBR with the partition table, the maximum size of its code is only 446 bytes. It first examines the partition table to discover the location of the first partition, and then reads the first 512 bytes – *containing the stage-1 bootloader* – from that partition into memory. Unfortunately, before the stage-1 bootloader can be executed, some additional data must also be read from the disk: a secondary structure called a *disklabel* (this is the standard disklabel used by DragonFly BSD [60]) stored immediately following the stage-1 bootloader. The disklabel is used to discover where the system images begin, as well as the location and size of the final stage of the bootloader code – the *stage-2 bootloader*. Once all of this data is read from disk, the stage-1 bootloader begins execution.

## 3.2.2 The Stage-1 Bootloader

The stage-1 bootloader examines the system RAM to build a map of the available memory, sets up segmentation and paging, enters long mode to enforce memory protection, and then passes control to the stage-2 bootloader. To build the

memory map, a BIOS call is invoked that returns a listing of available and reserved memory regions. Diagnostic information can be displayed at this point via a console that is enabled. Segmentation structures for the GDT and segment registers are created. A read-only code segment is created for both privilege levels 0 and 3 that stretches from 0 to the end of memory. Two read-write data segments are created in the same manner, and the segment selectors are initialized with these values. Finally, following the enabling of segmentation, protected and long mode are enabled: the low bit of CR0 is set, PAE mode for paging is enabled, and bits 8 and 11 of the EFER MSR (IA-32e mode, allow NX bit) are enabled.

Although the boot loader has set the necessary bits for entering long mode, it must also enable paging before long mode can be activated. To this end the first two megabytes of physical memory are identity-mapped to virtual memory, so that the physical and virtual addresses are equivalent. Finally, long mode is enabled by setting the paging bit of CR0, reloading the GDT with a new segmentation table (this table uses the same data, but with expanded sizes for the larger address space), and enabling the 64-bit code segment. The system is now in long mode, and the most basic requirements of modern operating systems have been satisfied; However, the bootloader has more work to do before the hypervisor can be started: Initially, the stage 1 bootloader enables the floatingpoint unit and vectorization units. Control is then passed to the stage-2 bootloader.

## 3.2.3 The Stage-2 Bootloader

The stage-2 bootloader is a much larger process that does not suffer from the 512-byte size limitation due to presence of paging. Unlike the MBR and stage1 bootloader, it is written entirely in C and performs tasks that require more complexity in code, which would result in a code fragments larger than 512 bytes. For example, since the system has entered long mode, convenient calls to the BIOS for basic tasks such as reading data from the disk and printing diagnostic messages can no longer be used. Thus, basic drivers for disk access and printing to the VGA memory must be included within this stage.

The stage-2 bootloader initially augments the already-paged memory: increasing the identity-mapped paged memory from the first two megabytes of system memory up to the first 12 megabytes, so that the hypervisor is guaranteed to fit when loaded. It then utilizes a basic IDE disk driver to read the hypervisor's ELF binary from the file system defined by the disklabel. Finally, the hypervisor's ELF structure is analyzed and checked by a minimal ELF loader. This loader performs no protection, relocation, or other complex tasks associated with normal user program loaders. Instead, it merely verifies the file for validity and loads the listed program headers. Once loaded, control passes to the entry point listed in the hypervisor binary. At this point, the boot process has completed.

Originally, the stage-2 bootloader also set up and handled a table of system interrupts. This functionality was eventually deemed unnecessary, and removed.

## 3.2.4 PXE Boot

The bootstrapping system described by Figure 3 is built upon a network boot protocol, called PXE boot, which runs before the MBR boot loader. The protocol downloads the image of a program named MEMDISK from a networked server [61]. This program transfers over the network a hard disk image containing the Bear operating system, which mirrors the structure and filesystem of the original physical hard disk. The MEMDISK program then copies the first 512 bytes of this disk image to physical address 0x7c00, just as the BIOS would do with the original physical hard disk. Then, the system begins executing the code or data as it originally did with the physical hard disk. The post-MEMDISK environment is indistinguishable to the environment seen by the bootloader without using network boot. However, any BIOS calls to disk reads are instead redirected by MEMDISK to the hard disk image in memory.

### **3.3 Goal 2: Kernel Refresh, Denying Persistence**

This section describes the hardware control and structures associated with virtualization on the Intel x86-64 platform and how these are used by the Bear hypervisor to operate virtual machines and perform kernel refresh. This feature set is commonly called Vt-x and the features are named in the Intel manual as VMX. Unlike many x86 features, Vt-x is **not** shared between Intel and AMD processors – AMD has its own hardware feature set for virtualization, called SVM. Bear initially targets Intel processors, and thus uses Intel VMX.

## 3.3.1 Enabling Virtualization

The virtualization feature set is controlled by the VMXE bit of the CR4 control register. To activate virtualization, this bit must be set; however, there are several subtleties that must also be observed. The abstract code in Program 1 describes the complete process.

```

// Check if VMX is available on this processor.

CPUID

Bit 5 in ECX set?

No -> Fail

// The BIOS can disable VMX. Test this, and enable VMX

// if it is not locked out.

Read MSR 0x3a

Bit 0 set, bit 2 cleared?

Yes -> Fail

Bit 0 set, bit 2 set?

Proceed

Bit 0 cleared, bit 2 cleared?

Set bits 0 and 2

// The VMXE bit must be enabled.

Set VMXE in CR4

// CR0 and CR4 must have specific bits set or cleared.

// Test that the values are what are needed for VMX.

tmp <- Read MSR 0x486

tmp = (CR0 AND tmp) XOR tmp

Is tmp 0?

No -> Fail

tmp <- Read MSR 0x487</pre>

tmp = (CR4 AND tmp) XOR tmp

Is tmp 0?

No -> Fail

// The processor uses a 4096-byte, page-aligned region

// of memory for storing information.

Allocate 4096-byte region of memory: VMX-Region

Zero VMX-Region

VMX-Region[0:29] <- MSR 0x480</pre>

VMXON VMX-Region

```

#### **Program 1: Enabling virtualization.**

On conclusion of this process, the processor is capable of utilizing virtualization. This includes launching, swapping, and resuming virtual machines. In this process, the hypervisor is called the *host* and the virtual machines it controls are called the *guests*. Launching or resuming a guest is called a *VM entry*, and control being passed back to the hypervisor is called a *VM exit*.

3.3.2 The Hypervisor Main Loop

Once virtualization is enabled through the process in section 3.3.1, the hypervisor is ready to launch and control the Bear microkernel. Program 2 describes the basic operation of the hypervisor. It consists of a simple loop that repeatedly creates a virtual machine, bootstraps the microkernel on a virtual machine from the read-only file store, waits for a preemption time, and nondeterministically discards the kernel.

```

// Initialize VMCS Region

START:

Allocate 4096-byte region of memory: VMCS

Zero VMCS

VMCLEAR VMCS

VMPTRLD VMCS

// Controlling parameters for the kernel are then set.

// These include a preemption timer, control register

// state, instruction pointer, and other values.

VMWRITE some-parameter

VMWRITE other-parameter

. . .

Load kernel from gold standard read-only source

Apply diversification

Save hypervisor register state

// Begin execution of virtual machine

VMLAUNCH VMCS

... virtual machine execution proceeds ...

... Preemption timer interrupt!

Save virtual machine register state

Restore hypervisor register state

Time for refresh?

-> Throw kernel away, goto START

Save hypervisor register state

Restore virtual machine register state

VMRESUME VMCS

```

#### Program 2: The hypervisor main loop.

A hypervisor controls its guests through a block of memory called the Virtual Machine Control Structure (VMCS). This is a four-kilobyte, page-aligned block of memory, one per logical virtual machine that the hypervisor executes. The VMCS contains all of the parameters associated with the guest that are manipulated in Program 2, including how the virtual machine might automatically be interrupted so as to pass control passed back to the hypervisor. There are a large number of parameters that can be stored in this structure, not all of which are used by the Bear system. The parameters used by the Bear system are listed and described in Appendix B; a complete listing can be found in [27].

In addition to the steps described in Program 2, there are several other necessary steps associated with bootstrapping a virtual machine. These include determining default and supported values for various VMCS fields; however, these are generally part of the initialization steps and not actively performed during the loading and managing of virtual machines and have no direct bearing on the project goals.

Recall that Program 2 refreshes the kernel from the RAM-disk corresponding to the gold-standard, read-only source to deny persistence. The read-only status of the disk is enforced by the hypervisor but could also be realized through a hardware back-channel to allow updates. This refresh-fromstandard process ensures that if a rootkit were to persist in the kernel's memory it will be flushed out of the system. By utilizing the read-only source, rootkits lose that avenue for persistence.

Although not yet described, it is valuable to understand the hook provided by Program 2 for applying the diversity ideas (Goal 6) that will emerge in later chapters: During the bootstrapping of a new kernel, the hypervisor uses an *ELF loader* that incorporates the ideas presented in Chapters 4 and 5.

## 3.3.3 Kernel Environment

The hypervisor initializes each kernel in an environment that acts as if a bootloader had initialized it. This environment mimics, in the kernel's memory space, all the normal attributes expected by a bootloader. System memory is placed in the same map; segmentation registers and paging are set up in the same manner (though diversity is added); long mode is enabled. Control registers are made to mimic those on the system. The parameter values used by the hypervisor are read and are set as those of the guest, the only change being that virtualization is disabled for the guest. Control register modification outside of these values is rendered impossible (see section 3.4.2).

The address space given to each guest mimics that given to the hypervisor by the bootloader, a 256-megabyte chunk of memory is allocated for each guest. This memory is redirected it so that the guest operates on physical addresses from zero to 256 MB (see section 3.4.1 for more details on this process). A BIOS memory map is placed at the normal bootloader location, marking the BIOS areas as unavailable and the rest of the space as available for system use. Unlike the hypervisor bootloader however, the hypervisor employs a sophisticated and fullfeatured ELF loader. This enables the hypervisor to apply diversity to the kernel's ELF binary, both the kernel code and data scattered throughout its address space. For more information on this process and the details of the scattering, see chapters 4 and 5.

Some spaces external to the guests 256-megabyte chunk are redirected into the kernel memory space. The VGA memory used by the console is placed in its normal physical location. Any memory for the network card and, theoretically in the future, other hardware peripherals, is likewise redirected and available for use directly by the kernel. The hypervisor does not attempt to multiplex access to hardware contested by its guests: instead, it operates under the assumption that only one kernel will be active and have access to hardware at any given time. Recall that the hypervisor exists only to non-deterministically throw away kernels and refresh them from a gold standard, removing persistence in the kernel. With no contention for hardware, the hypervisor is not required to mediate access, keeping its code base minimal<sup>2</sup>.

### **3.4 Goal 3: MULTICS-style Protections Applied to Kernels**

Recall that design Goal 3 involves applying classic MULTICS-style read/write/execute protections to kernel memory. These protections prevent accidental and malicious memory corruption by writing into executable code.

Running guests in paged protected mode while preserving the illusion that they have complete control over the system, has classically been a thorny issue. A guest kernel running unmodified would clearly need to exert some form of control over the system page tables in order to allocate its own memory and separate user processes from each other. Giving the guest total control, however, would defeat the point of the hypervisor providing protections and isolating guests: the guest could examine and modify any memory on the system, including that used by the

$<sup>^{2}</sup>$  Eventually, some form of validity checking with how a kernel interacts with the hardware may be implemented. If this is done, the hypervisor will need to mediate access – but in this case, for protection, not multiplexing.

hypervisor to control the guest. The hypervisor would then be unable to protect kernels in the same fashion as kernels protect user processes.

Past solutions have centered on *shadow page tables*, where the guest kernel is unable to actually access the page tables. The hypervisor keeps a mapping of virtual memory as seen by the guest and its correct translation to physical memory. Any attempt to modify CR3 or the page tables would cause a VM exit, and the hypervisor would then handle the modification instead after checking that it was acceptable. Any page fault would similarly be forwarded to the hypervisor, which would need to service the interrupt. This process is *slow* and puts the burden for checking whether a modification is benign (a process switch) or malicious (making hypervisor memory accessible to the kernel) onto the hypervisor. It also significantly increases the complexity of the hypervisor, which then needs to incorporate knowledge of how to deal with the memory management systems of each guest kernel that might need to run.

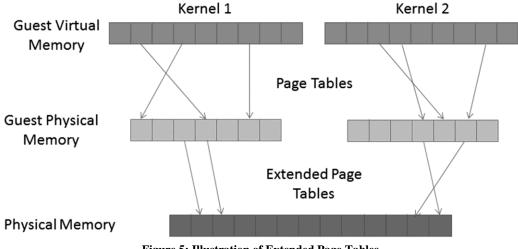

To deal with these issues, Intel released the *Extended Page Table* system. This is a form of nesting where the guest has complete control over the classic page table structure. The hypervisor provides an extra layer of address translation, after the normal page tables, which is completely transparent to the guest operating system. This allows a hypervisor to manage physical memory without the overhead of shadow page tables while also giving the guest the illusion of total physical memory access. A diagram of the resulting translation system can be seen in Figure 5.

35

Figure 5: Illustration of Extended Page Tables.

Addresses are translated from *guest virtual* to *guest physical* using the normal page table structure of the kernel. Afterward, a second page table structure takes over which translates the guest physical address to its true physical address. This structure is rooted by the *Extended Page Table Pointer* (EPTP). The EPTP is defined in the VMCS, and is the EPT version of CR3. Much like the rest of the system, an EPT page can be configured to be either four kilobytes or two megabytes large, with the length of translation and page table structures changing accordingly. The Bear system uses a four kilobyte page size for both the normal page tables and the EPT.

Similar to how the kernel allocates memory for user processes, the hypervisor can decide which system memory it exposes to running guests. This choice generally excludes the memory of itself and other virtual machines on the system, thus offering isolation and protection. A kernel cannot view other memory on the system without modifying the hypervisor's EPT structure, which it cannot do without somehow breaking into the hypervisor. While EPT has vastly simplified hypervisor logic, it comes with another benefit – built-in MULTICS protections. EPT, just like the normal page tables, allows the hypervisor to control which among read/write/execute permissions are allowed for a given memory page. With the desired read/write/execute permissions for memory segments set in the ELF binary for the kernel, these MULTICS-style protections can be applied to the kernel, just as the kernel applies them to its own running processes.

The Bear hypervisor configures EPT to provide these controls on kernel code and data, learning from the kernel's ELF binary which pages should be protected to what degree. If there were no hypervisor, an exploit with kernel-level access could modify the page tables to perform these operations at will. With the addition of the hypervisor, however, any attempt to patch read-only kernel memory or execute code located in a data region will result in a VM exit, at which point the hypervisor can take appropriate action. Hypervisor memory is inaccessible from the guest; using EPT, it does not even need to be mapped into the guest's address space. The abstract code for the hypervisor is thus augmented as shown in Program 3.

37

// Begin execution of virtual machine VMLAUNCH VMCS ... virtual machine execution proceeds ... ... EPT violation interrupt! Save virtual machine register state Restore hypervisor register state // Take appropriate action. One possibility: Log violation Put kernel in background; accepts no new connections. // Start a new kernel to handle new clients. Goto START // Restore the bad kernel on an unused processor. Restore virtual machine register state VMRESUME VMCS

The mechanism whereby a hypervisor might spin down a kernel with outstanding connections until their completion, while spinning up a new goldstandard kernel for new connections, is explored in [56].

## 3.5 Goal 4: Processor State Protection

The intent of protecting the processor state is to prevent successful exploits from performing modifications that would assist with stealth and persistence. By virtue of adding another layer of hardware controls to the system, hypervisors can provide protections to kernels that were previously impossible. The ability to provide MULTICS-style protections has already been discussed, but there are also additional mechanisms available to protect the processors critical data structures. As these structures are often used by rootkits to aid in stealth, protections on them can mitigate fundamental attacks against memory protections. For example, consider the "CR0 trick" [10] used to bypass system memory protections: The x86 architecture contains a flag in CR0 which, if cleared, allows kernel-level code to write to any region of memory, *even write-protected memory*. Since kernel-level code can modify CR0, any malicious code that wishes

to write to read-only memory need only clear the WP bit, perform the desired writes, and reset the bit once more, entirely bypassing any form of writeprotection that has been set in the segment registers or page tables.

With hypervisor protections on the control registers, this attack can be eliminated. Using specific fields in the VMCS (see Appendix B for more details on these fields: the **guest/host mask** and **read shadow**), the hypervisor can set this bit to a static value that a kernel cannot change. Then, a malicious attempt to clear the bit will cause a *VMexit*, preventing undesired writes to read-only memory<sup>3</sup>.

Unfortunately, these protections are not general-purpose in nature; many operating systems, including the Bear bootloader, utilize write protection bypass feature in their own code. Thus, to properly utilize these protections, the kernel must be designed with the inability to bypass the restrictions in mind. Even if the hypervisor enforces the condition that code to *disable* the protections was only to be run within a specific function, malicious code could always return to that function in a return-to-libc style attack, and then proceed. To ensure complete write protection within kernels, the ability to bypass it at all must be removed. For the Bear system, any possibility of disabling these write protections has been

<sup>&</sup>lt;sup>3</sup> It's worth remembering that there are other ways to bypass write protections in the Intel system, not just the CR0 trick. For example, the page table entries could be modified, by setting the writable bits in the individual entry or creating a whole new page structure. Both of these can also be controlled by the hypervisor though: either through use of EPT in the former or both EPT and the CR3 controls in the latter.

removed – with the ability completely out of the kernel's hand, any such returnto-libc style attack is taken off the table.

## 3.6 Attack Surface Minimization

The Bear system has been designed to minimize the attack surface by extensively sharing code between the hypervisor and microkernel. Recall that a survey of open source code discovered approximately 0.16 errors per thousand lines of code in open source software [52], making the reduction of the attack size a laudable goal for reducing vulnerabilities. Table 1 shows the current number of unique lines of code in each component of the Bear system, as well as shared lines of code.

Table 1: Code size.

| Component  | Lines of Code |

|------------|---------------|

| Hypervisor | 1,788         |

| Kernel     | 2,335         |

| Shared     | 5,062         |

The shared code includes the following:

- Basic data structures (queue, hash table, etc.).

- Interrupts handling

- C-callable wrappers around basic assembler instructions.

- Virtual memory subsystem, including allocation and freeing.

- Disk access (including RAM disk) and filesystem.

- System timer.

- The ELF loader.

- Process scheduler (schedules both user processes and virtual machines).

## **3.7 Supporting Legacy Operating Systems**

A future research project involves the running of different operating systems on the Bear hypervisor. This work is still in its vestigial stages and is experimental, as the Bear hypervisor was originally designed solely to run the Bear kernel. The first operating system that has been run on Bear is NetBSD version 6.0.1.

Unlike running the Bear kernel, for NetBSD the hypervisor does not perform any of the boot loader operations that the kernel expects to have been performed. Segmentation and long mode are not enabled; instead, the guest is started in real mode as if the system had just been booted – though a memory map is provided as if performed by BIOS call. The system BIOS memory is copied into the address space of the guest, so the guest may directly perform any BIOS calls that it might need without hypervisor interference; otherwise, the hypervisor would need to emulate a large number of complex BIOS routines. Multiprocessing is **not** supported: while the ACPI region of the BIOS memory reports that multiple processing cores are available, NetBSD has been compiled and passed flags to disable this behavior and instead run on a single core, without using ACPI at all. The current status of the project is that NetBSD successfully boots, but does not start a shell due to lack of a root file system -- Bear no longer supports a physical disk. To mitigate this involves porting NFS and pointing it to an NFS share across the network to act as its root filesystem.

This work has only been possible due to the open nature of NetBSD; a similar attempt to virtualize Microsoft Windows would likely prove to be much

41

more complex due to the inability to examine the Windows source code when problems arise with virtualization.

## 3.8 Summary

In summary, this chapter has described a minimalist hypervisor that continually refreshes kernels to deny persistence. The hypervisor shares code extensively with the microkernel, applies MULTICs-style read/write/execute protections to kernels and additional protections on the processor state. Write protection is enabled through the hardware NX-bit in X86-64 page table entries. The protections are leveraged to support a diskless, real-only bootstrapping process. The hypervisor main loop provides the necessary hooks for adding diversity every time a new kernel is refreshed.

# **Chapter 4: Diversity through Compile-Time Techniques**

Diversification is the primary mechanism for preventing unexpected code execution and similar exploits in the Bear system. The diversifying transformations nondeterministically scramble the locations of code and data on the system, making exploits that rely on this knowledge fail. The process of introducing nondeterministic modifications to binaries also serves to create differences between running versions of code on networked systems and thus throttle the *vulnerability amplification* aspect of networks such as the Internet. With each system running something different, attackers must craft new exploits to target specific systems, rather than a single exploit for every system.

The Bear diversifying transformations seek to achieve four key properties in the resulting binary codes:

- 1. Shifting all code out of position to disrupt the *entry points* for all code segments, including unanticipated ones.

- 2. Placing all code in an unpredictable location to prevent an attack from *resuming* to normal execution by jumping or returning to a known location.

- 3. Changing jump offsets within all code paths, such as *if/else*, *switch*, and *for*-loop blocks, to remove similarities between all variants of a binary.

4. Shifting of all data out of position to disrupt direct manipulation.

Properties #1 and #2 prevent code execution that hijack pre-existing code on a system, such as Return-Oriented Programming [14]. Property #2 denies *persistence* on the system, disallowing an attacker from achieving a hidden pointof-presence within a running system. Property #3 enhances diversity beyond ASLR [32], extending the entropy to *logical blocks* within the program rather than simply individual functions or ELF segments. Property #4 removes the ability to designate control or plant code in pre-existing data structures.

Compile-time diversification is performed through two operations: the *padding transformation* and the *ordering transformation*.

## 4.1 Implementation

The compile-time diversity techniques are introduced as part of the compiler toolchain. The padding transformation is implemented as a Clang compiler plugin [62], and the ordering transformation is implemented as a patch to GNU Gold, a linker that is part of the standard GNU Binutils package [26] on Linux systems. To add diversity to a binary, the compilation process must be slightly modified in two stages:

- Before normal compilation with the C compiler (such as gcc), the source files must be diversified via the clang plugin. This represents as a precompilation pass, and applies the padding transformation.

- The linker requires an additional flag passed as part of the linking process:

"--randomize-text". This tells the linker to apply the ordering transformation to the final output.

The resulting binary is identical in function to a binary compiled without diversity, but has been nondeterministically modified to satisfy goals 1, 2, and 3.

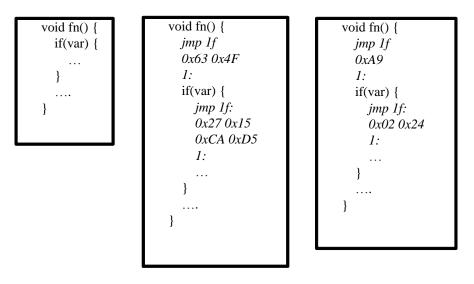

4.1.1 The Padding Transformation

Recall that the diversity transformations are motivated by three core goals: disruption of *entry points*, disruption of return points for *resuming normal execution*, and modification of all *jump offsets* within code paths. To achieve each of these ideas, *s* bits of entropy are injected into every *block* in a program. This is achieved by inserting a random number of bytes, between 0 and  $2^{s} - 1$ , at the beginning of each block, using a uniform random distribution. The inserted bytes themselves are random numbers. Jump instructions are inserted before the random byte stream to ensure they are not executed by normal operation; this minimizes the performance effect of the transformation. The insertion is implemented through source-to-source transformation on the original C source code using a Clang compiler plug-in. The plug-in operates as shown in Program 4.

```

For each source file:

For each function:

n <- random(0, 2<sup>s</sup> - 1)

insert_asm_string("jmp 1f")

for i from 0 to n:

b <- random(0, 255)

insert_asm_string(".byte b")